Difference between revisions of "Tutorial:HPCA 2013 Sniper"

| (3 intermediate revisions by one other user not shown) | |||

| Line 1: | Line 1: | ||

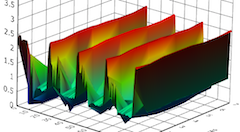

[[File:Level3vis.png|frame|right|Visualization in Sniper 4.1]] | [[File:Level3vis.png|frame|right|Visualization in Sniper 4.1]] | ||

| + | |||

| + | ==Tutorial Complete== | ||

| + | The Sniper team was really happy with the turnout for our HPCA tutorial this year. Below, you will find a copy of the tutorial slides. Please feel free to contact us anytime if there are additional questions about Sniper. | ||

| + | |||

| + | ==Slides== | ||

| + | [http://snipersim.org/documents/2013-02-23%20Sniper%20HPCA%20Tutorial.pdf HPCA Tutorial Slides] | ||

==Location and Date== | ==Location and Date== | ||

| Line 34: | Line 40: | ||

[[The Sniper Multi-Core Simulator|Sniper's]] key features are: | [[The Sniper Multi-Core Simulator|Sniper's]] key features are: | ||

* The interval core model to raise the level of abstraction in multi-core simulation | * The interval core model to raise the level of abstraction in multi-core simulation | ||

| − | * Parallel simulation on multi-core host hardware | + | * Parallel simulation on multi-core host hardware, achieving simulation speeds of up to 2 MIPS |

| − | * Runs multi-threaded shared-memory x86 workloads | + | * Runs multi-threaded shared-memory and multi-programmed x86 workloads |

| − | * | + | * Support for heterogeneous configurations, thread scheduling and migration |

* Validated against real hardware | * Validated against real hardware | ||

Additional information about Sniper can be found [[The Sniper Multi-Core Simulator|here]]. | Additional information about Sniper can be found [[The Sniper Multi-Core Simulator|here]]. | ||

| − | == | + | ==Schedule== |

| − | * Sniper | + | * 09:00-09:30 Introduction & Sniper rationale |

| − | * Interval | + | * 09:30-10:00 Interval core model |

| − | * | + | * 10:00-10:30 — Coffee break — |

| − | * | + | * 10:30-10:45 Validation results |

| − | * | + | * 10:45-11:30 Running simulations & processing results |

| − | + | * 11:30-12:00 Visualization & demo | |

| − | * | ||

==Biographies== | ==Biographies== | ||

Latest revision as of 22:20, 23 February 2013

Tutorial Complete

The Sniper team was really happy with the turnout for our HPCA tutorial this year. Below, you will find a copy of the tutorial slides. Please feel free to contact us anytime if there are additional questions about Sniper.

Slides

Location and Date

We will give a tutorial on Sniper at HPCA 2013 in Shenzhen, China. The tutorial is scheduled for the morning of Saturday, February 23 in the Madrid 2 conference room.

Organizers and Presenters

Organizer: Lieven Eeckhout, Ghent University

Presenter: Wim Heirman, Intel ExaScience Lab and Ghent University

Presenter: Trevor E. Carlson, Intel ExaScience Lab and Ghent University

Presenter: Kenzo Van Craeynest, Ghent University

Abstract

Two major trends in high-performance computing, namely, larger numbers of cores and the growing size of on-chip cache memory, are creating significant challenges for evaluating the design space of future processor architectures. Fast, scalable and accurate simulations are needed to allow for sufficient exploration of large multi-core systems within a limited simulation time budget. Through the use of high-abstraction analytical models with fast parallel simulation in the Sniper simulator, computer architects can trade off accuracy with simulation speed to allow for longer application runs, covering a larger portion of the hardware design space.

The purpose of this tutorial is to introduce both the main features of the Sniper simulator, as well as provide detail into the use of the simulator itself. Specifically, this tutorial will provide an in-depth look into the theory and implementation of the interval core model and CPI-stack generation. We will give a detailed rundown of how to specify heterogeneous architectures and implement scheduling algorithms. We also highlight other features such as full DVFS support, scripting and program-to-simulator communication and provide an overview of the various component models and simulator configurability and flexibility.

Sniper's key features are:

- The interval core model to raise the level of abstraction in multi-core simulation

- Parallel simulation on multi-core host hardware, achieving simulation speeds of up to 2 MIPS

- Runs multi-threaded shared-memory and multi-programmed x86 workloads

- Support for heterogeneous configurations, thread scheduling and migration

- Validated against real hardware

Additional information about Sniper can be found here.

Schedule

- 09:00-09:30 Introduction & Sniper rationale

- 09:30-10:00 Interval core model

- 10:00-10:30 — Coffee break —

- 10:30-10:45 Validation results

- 10:45-11:30 Running simulations & processing results

- 11:30-12:00 Visualization & demo

Biographies

Lieven Eeckhout is a Professor at Ghent University, Belgium, in the Department of Electronics and Information Systems (ELIS). He obtained his MS and PhD degrees from Ghent University in 1998 and 2002, respectively. His research interests include computer architecture and the hardware/software interface in general, and performance analysis, evaluation and modeling more in particular. He received two IEEE Micro Top Picks Awards and recently wrote a synthesis lecture on "Computer Architecture Performance Evaluation Methods" published by Morgan and Claypool. He graduated 7 PhD students, and currently supervises 4 postdoctoral researchers and 8 PhD students.

Wim Heirman received his PhD in 2008 from Ghent University, Belgium, on reconfigurable optical interconnection networks for multicore processors. Since 2010, Dr. Heirman has worked at the Intel Exascience Laboratory. His research interests are fast and accurate computer simulation, enabling architectural exploration and software analysis through co-design, and energy-efficient high-performance computing.

Trevor E. Carlson is a PhD student at Ghent University and is a part of the Intel ExaScience Lab. He received his BS and MS degrees from Carnegie Mellon University in 2002 and 2003, respectively. He has previously served as a Staff Engineer at IBM where he helped to author 4 issued patents and also served as a Researcher at IMEC where he investigated efficient architectures for embedded and 3D-stacked systems. His research interests include performance modeling and fast and scalable simulation methodologies.

Kenzo Van Craeynest is a PhD student at Ghent University where he also received his masters in computer science in 2008. His research interests include cache performance, performance modeling, heterogeneous multi-cores and thread scheduling.

Related Tutorials

- Deterministic PinPoints tutorial at HPCA on February 23rd in the afternoon (right after the Sniper tutorial)