Difference between revisions of "The Sniper Multi-Core Simulator"

| Line 18: | Line 18: | ||

[[Paper:Sc2011Carlson|Sniper]] is | [[Paper:Sc2011Carlson|Sniper]] is | ||

| − | a next generation | + | a next generation parallel, high-speed and accurate |

| − | x86-64 simulator. This | + | x86-64 simulator. This multi-core simulator is |

based on the [[Interval Simulation|interval core model]] and the [http://groups.csail.mit.edu/carbon/graphite Graphite] simulation | based on the [[Interval Simulation|interval core model]] and the [http://groups.csail.mit.edu/carbon/graphite Graphite] simulation | ||

infrastructure, allowing for fast and accurate simulation and for | infrastructure, allowing for fast and accurate simulation and for | ||

trading off simulation speed for accuracy to allow a range of flexible | trading off simulation speed for accuracy to allow a range of flexible | ||

| − | simulation options when exploring different | + | simulation options when exploring different multi-core architectures. |

Using this methodology, we are able to achieve good | Using this methodology, we are able to achieve good | ||

accuracy against hardware for 16-thread applications. | accuracy against hardware for 16-thread applications. | ||

| Line 31: | Line 31: | ||

at a high speed when compared to existing simulators. The main | at a high speed when compared to existing simulators. The main | ||

feature of the simulator is its core model which is based on the [[Interval Simulation|interval core model]], | feature of the simulator is its core model which is based on the [[Interval Simulation|interval core model]], | ||

| − | a fast mechanistic core model. | + | a fast mechanistic core model. The interval model raises the level |

| − | + | of abstraction in architectural simulation which allows for faster | |

| − | between miss events | + | simulator development and evaluation times; it does so by 'jumping' |

| − | On recent | + | between miss events, called intervals. On recent multi-core hardware, |

| + | we see speeds of up to 2 MIPS | ||

for SPLASH-2 benchmarks, and almost 3 MIPS for SPEC OMP benchmarks. | for SPLASH-2 benchmarks, and almost 3 MIPS for SPEC OMP benchmarks. | ||

Revision as of 01:19, 11 January 2012

April 1st: Sniper tutorial at ISPASS'12

June 9th: Sniper tutorial at ISCA'12

Sniper is a next generation parallel, high-speed and accurate x86-64 simulator. This multi-core simulator is based on the interval core model and the Graphite simulation infrastructure, allowing for fast and accurate simulation and for trading off simulation speed for accuracy to allow a range of flexible simulation options when exploring different multi-core architectures. Using this methodology, we are able to achieve good accuracy against hardware for 16-thread applications.

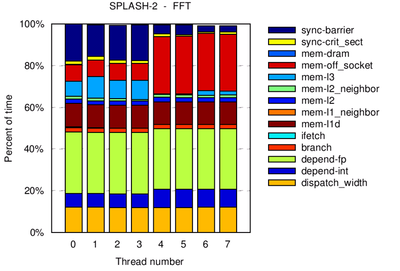

The Sniper simulator allows one to perform timing simulations for multi-threaded, shared-memory applications with 10s to 100+ cores, at a high speed when compared to existing simulators. The main feature of the simulator is its core model which is based on the interval core model, a fast mechanistic core model. The interval model raises the level of abstraction in architectural simulation which allows for faster simulator development and evaluation times; it does so by 'jumping' between miss events, called intervals. On recent multi-core hardware, we see speeds of up to 2 MIPS for SPLASH-2 benchmarks, and almost 3 MIPS for SPEC OMP benchmarks.

This simulator, and the interval core model, is useful for uncore and system-level studies that require more detail than the typical one-IPC models. As an added benefit, the interval core model allows the generation of CPI stacks, which shows the number of cycles lost due to different characteristics of the system, like the cache hierarchy or branch predictor, to be easily understood.

Features

In addition to the main features mentioned above, we have updated the base simulation infrastructure to allow for simulating a larger set of workloads on more recent simulated hardware. Here is the full set of some of the recently added features:

- Interval core model

- CPI Stacks to gain insight into lost cycles

- Parallel, multithreaded simulator

- Multithreaded application support, x86-64, SSE2

- Validated against the Intel Core 2 and Nehalem/Westmere microarchitectures

- Full DVFS support

- Shared and private caches

- Modern branch predictor

- Supports parallel applications using pthreads, OpenMP, TBB, OpenCL

- Runs SPLASH-2, Rodinia, SPEC OMP and most of PARSEC

- SimAPI and Python interfaces for monitoring and controlling the simulator's behavior at runtime

- Easy debugging of applications and the simulator

- Multiple Linux-OS support (Redhat/Debian/Ubuntu/etc.)

- Open source software, licensed under the MIT and the Interval Academic License

- Additional features

You can find additional information on the simulator and its components in our recently accepted SC'11 paper.

Getting started

- Download the Sniper source code

- Follow the Getting Started instructions

- View the Frequently Asked Questions

- Attend our tutorial at ISPASS'12 or ISCA'12

Discussion list

| Subscribe to the Snipersim mailing list |

| Email: |

Please send any questions or comments to: snipersim [at] groups [dot] google [dot] com . You can also visit our Google Groups page to subscribe to the list and search through the archive of previous messages.

Team Members

- Trevor E. Carlson with the Intel ExaScience Lab and Ghent University

- Wim Heirman with the Intel ExaScience Lab and Ghent University

- Lieven Eeckhout with Ghent University

More information

<meta name="keywords" content="Sniper Simulator,Sniper,simulator,computer architecture,multicore,multi core,multi-core,manycore,many core,many-core,micro-architecture,microarchitecture,ExaScience Lab,exascience,exascale,SC11,supercomputers,super-computing,computers,Ghent University,Universiteit Gent"/>