Difference between revisions of "The Sniper Multi-Core Simulator"

| (155 intermediate revisions by 2 users not shown) | |||

| Line 1: | Line 1: | ||

| − | + | <div style="text-align: left; border: 2px solid #FFE97F; margin: 1em 0 1em 0; padding: .5em 1ex .5em 10ex; background-color:#FFF6D6"> | |

| − | + | ||

| − | + | Sniper 8.0 is now available on [https://github.com/snipersim/snipersim GitHub] and [https://hub.docker.com/r/snipersim/snipersim DockerHub] | |

| − | based on the [[Interval | + | |

| + | Version 7.3 of [[Releases|Sniper has been released]]. It has support for Ubuntu 18.04, GCC 7, Pin 3.10+, and [https://carrv.github.io/2018/papers/CARRV_2018_paper_7.pdf initial support for RISC-V]. | ||

| + | |||

| + | An initial implementation of [https://github.com/trevorcarlson/barrierpoint BarrierPoint] had been released. | ||

| + | |||

| + | [https://sites.google.com/site/pinpointstutorialisca14 PinPoints Tutorial at ISCA] with Sniper. Learn about PinPoints or [[Pinballs|download SPEC CPU2006 pinballs]] | ||

| + | |||

| + | The FOSDEM 2014 video of the Sniper tutorial is [[FOSDEM_2014|now available to view]] | ||

| + | |||

| + | [[Tutorial:IISWC_2013_Sniper|Sniper tutorial at IISWC]] | ||

| + | |||

| + | </div> | ||

| + | |||

| + | [[Paper:Sc2011Carlson|Sniper]] is | ||

| + | a next generation parallel, high-speed and accurate | ||

| + | x86 simulator. This multi-core simulator is | ||

| + | based on the [[Interval Simulation|interval core model]] and the [https://github.com/mit-carbon/Graphite Graphite] simulation | ||

infrastructure, allowing for fast and accurate simulation and for | infrastructure, allowing for fast and accurate simulation and for | ||

trading off simulation speed for accuracy to allow a range of flexible | trading off simulation speed for accuracy to allow a range of flexible | ||

| − | simulation options when exploring different | + | simulation options when exploring different homogeneous and heterogeneous multi-core architectures. |

| − | |||

| − | |||

| − | |||

| − | The Sniper simulator allows one to perform timing simulations for | + | The Sniper simulator allows one to perform timing simulations for both multi-program workloads |

| − | multi-threaded, shared-memory applications with 10s to 100+ cores, | + | and multi-threaded, shared-memory applications with 10s to 100+ cores, |

at a high speed when compared to existing simulators. The main | at a high speed when compared to existing simulators. The main | ||

| − | feature of the simulator is its core model which is based on | + | feature of the simulator is its core model which is based on [[Interval Simulation|interval simulation]], |

| − | a fast mechanistic core model. | + | a fast mechanistic core model. Interval simulation raises the level |

| − | + | of abstraction in architectural simulation which allows for faster | |

| − | + | simulator development and evaluation times; it does so by 'jumping' | |

| + | between miss events, called intervals. | ||

| + | Sniper has been validated against multi-socket Intel Core2 and Nehalem systems | ||

| + | and provides average performance prediction errors within 25% | ||

| + | at a simulation speed of up to several MIPS. | ||

This simulator, and the interval core model, is useful for uncore | This simulator, and the interval core model, is useful for uncore | ||

and system-level studies that require more detail than the typical | and system-level studies that require more detail than the typical | ||

| − | one-IPC models. | + | one-IPC models, but for which cycle-accurate |

| − | the generation of CPI stacks, which | + | simulators are too slow to allow workloads of meaningful sizes to be simulated. |

| + | As an added benefit, the interval core model allows | ||

| + | the generation of CPI stacks, which show the number of cycles lost | ||

due to different characteristics of the system, like the cache | due to different characteristics of the system, like the cache | ||

| − | hierarchy or branch predictor, to | + | hierarchy or branch predictor, and leads to a better understanding of each component's |

| + | effect on total system performance. This extends the use for Sniper | ||

| + | to application characterization and hardware/software co-design. | ||

=== Features === | === Features === | ||

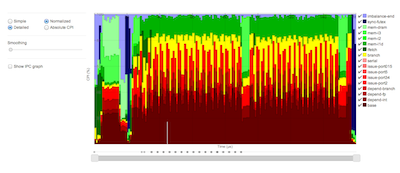

| − | + | [[File:Level2vis400.png|right|CPI stack visualization in Sniper 4.1|link=http://snipersim.org/viz/fft-tiny-4/levels/level2/cyclestacks.html]] | |

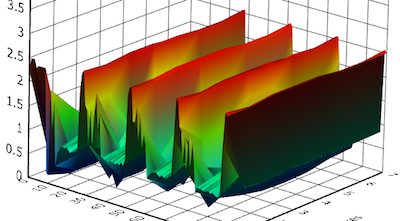

| + | [[File:Level3vis400.png|right|IPC visualization in Sniper 4.1|link=http://snipersim.org/viz/fft-tiny-4/levels/level3/level3.html]] | ||

In addition to the main features mentioned above, we have updated | In addition to the main features mentioned above, we have updated | ||

the base simulation infrastructure to allow for simulating a larger | the base simulation infrastructure to allow for simulating a larger | ||

set of workloads on more recent simulated hardware. Here is the full | set of workloads on more recent simulated hardware. Here is the full | ||

set of some of the recently added features: | set of some of the recently added features: | ||

| − | * [[Interval | + | * [[Interval Simulation|Interval core model]] |

| − | * [[CPI Stacks]] to gain insight into lost cycles | + | * [[Paper:Taco2014Carlson|Instruction-Window Centric core model, supporting in-order, out-of-order and SMT cores]] |

| − | * | + | * [[Paper:Ispass2013Carlson|Multi-threaded application sampling support]] |

| − | * Validated against the Intel Core 2 | + | * [[CPI Stacks]] and [http://snipersim.org/viz/fft-tiny-4/ advanced visualization support] to gain insight into lost cycles |

| + | * Parallel, multi-threaded simulator | ||

| + | * [[Multi-programmed workloads|Multi-program]] and multi-threaded application support, x86 and x86-64, SSE2 | ||

| + | * Validated against the Intel Core 2 microarchitecture (See the [[Frequently Asked Questions|FAQ]] for details) | ||

* Full DVFS support | * Full DVFS support | ||

* Shared and private caches | * Shared and private caches | ||

| + | * Prefetchers | ||

| + | * Scheduling support | ||

| + | * [[Heterogeneous Configuration|Heterogeneous configuration support]] | ||

* [http://dx.doi.org/10.1109/ISPASS.2009.4919652 Modern branch predictor] | * [http://dx.doi.org/10.1109/ISPASS.2009.4919652 Modern branch predictor] | ||

| − | * OpenMP | + | * Supports parallel applications using pthreads, OpenMP, TBB, OpenCL |

| − | * Runs SPLASH-2, Rodinia, SPEC | + | * Runs SPLASH-2, Rodinia, SPEC OMP and most of PARSEC (See our [[Download Benchmarks|integrated benchmarks quick-start guide]]) |

| − | * SimAPI for | + | * [[McPAT]] integration |

| − | * | + | * SimAPI and Python interfaces for monitoring and controlling the simulator's behavior at runtime |

| − | * | + | * Single-option debugging of simulator or the application itself |

| − | * Open source software, [[License|licensed]] under the MIT and Interval Academic License | + | * Modern Linux-OS support (Redhat EL 5,6/Debian Lenny+/Ubuntu 10.04-15.04+/etc.) |

| + | * Open source software, [[License|licensed]] under the MIT and the Interval Academic License | ||

* [[Sniper Features|Additional features]] | * [[Sniper Features|Additional features]] | ||

| − | You can find additional information on the simulator and its components in our | + | You can find additional information on the simulator and its components in our [[Paper:Taco2014Carlson|TACO]] or [[Paper:Sc2011Carlson|SC'11 paper]]. |

=== Getting started === | === Getting started === | ||

| − | * [[Download]] the Sniper source code | + | * [[Download]] the Sniper source code (Git and download options) |

* Follow the [[Getting Started]] instructions | * Follow the [[Getting Started]] instructions | ||

| + | * Take a look at the [[Manual|Sniper Manual]] | ||

| + | * View the [[Frequently Asked Questions]] | ||

| + | * Review the [http://snipersim.org/documents/2013-01-22%20Sniper%20HiPEAC%20Tutorial.pdf slides from our latest tutorial] | ||

| + | * View our most recent [[Releases|simulator updates]] | ||

| + | * If you are using a modern version of Sniper, please cite our [[Paper:Taco2014Carlson|TACO paper (bibtex)]] | ||

=== Discussion list === | === Discussion list === | ||

| − | Please send any questions or comments to: <code>snipersim [at] | + | <html><div style="float:right"><table border=0 cellspacing=0> |

| + | <tr><td style="padding-left: 5px"> | ||

| + | <b>Subscribe to the Snipersim mailing list</b> | ||

| + | </td></tr> | ||

| + | <form action="https://groups.google.com/group/snipersim/boxsubscribe"> | ||

| + | <tr><td style="padding-left: 5px;"> | ||

| + | Email: <input type=text name=email> | ||

| + | <input type=submit name="sub" value="Subscribe"> | ||

| + | </td></tr> | ||

| + | </form> | ||

| + | </table></div></html> | ||

| + | |||

| + | Please send any questions or comments to: <code>snipersim [at] googlegroups [dot] com</code> . You can also visit our [http://groups.google.com/group/snipersim Google Groups] page to subscribe to the list and search through the archive of previous messages. | ||

| + | |||

| + | <html><div style="clear:both"></div></html> | ||

=== Team Members === | === Team Members === | ||

| − | * [ | + | * [https://comp.nus.edu.sg/~tcarlson Trevor E. Carlson] with [http://nus.edu.sg National University of Singapore] |

| − | * [http://www.elis.ugent.be/~wheirman Wim Heirman] | + | * [http://www.elis.ugent.be/~wheirman Wim Heirman] with the [http://exascience.com Intel ExaScience Lab] |

| − | * [http://www.elis.ugent.be/~leeckhou Lieven Eeckhout] | + | * [http://www.elis.ugent.be/~leeckhou Lieven Eeckhout] with [http://www.ugent.be Ghent University] |

| + | * [mailto:ibrahim.hur@intel.com Ibrahim Hur] with the [http://exascience.com Intel ExaScience Lab] | ||

| + | |||

| + | === More information === | ||

| + | * [[Publications using Sniper]] | ||

| + | * [[Sniper Tutorials]] | ||

| − | < | + | <metadesc>Sniper Simulator,Sniper,simulator,computer architecture,multicore,multi core,multi-core,manycore,many core,many-core,micro-architecture,microarchitecture,ExaScience Lab,exascience,exascale,SC11,supercomputers,super-computing,computers,Ghent University,Universiteit Gent</metadesc> |

__NOTOC__ | __NOTOC__ | ||

Latest revision as of 17:55, 5 September 2023

Sniper 8.0 is now available on GitHub and DockerHub

Version 7.3 of Sniper has been released. It has support for Ubuntu 18.04, GCC 7, Pin 3.10+, and initial support for RISC-V.

An initial implementation of BarrierPoint had been released.

PinPoints Tutorial at ISCA with Sniper. Learn about PinPoints or download SPEC CPU2006 pinballs

The FOSDEM 2014 video of the Sniper tutorial is now available to view

Sniper is a next generation parallel, high-speed and accurate x86 simulator. This multi-core simulator is based on the interval core model and the Graphite simulation infrastructure, allowing for fast and accurate simulation and for trading off simulation speed for accuracy to allow a range of flexible simulation options when exploring different homogeneous and heterogeneous multi-core architectures.

The Sniper simulator allows one to perform timing simulations for both multi-program workloads and multi-threaded, shared-memory applications with 10s to 100+ cores, at a high speed when compared to existing simulators. The main feature of the simulator is its core model which is based on interval simulation, a fast mechanistic core model. Interval simulation raises the level of abstraction in architectural simulation which allows for faster simulator development and evaluation times; it does so by 'jumping' between miss events, called intervals. Sniper has been validated against multi-socket Intel Core2 and Nehalem systems and provides average performance prediction errors within 25% at a simulation speed of up to several MIPS.

This simulator, and the interval core model, is useful for uncore and system-level studies that require more detail than the typical one-IPC models, but for which cycle-accurate simulators are too slow to allow workloads of meaningful sizes to be simulated. As an added benefit, the interval core model allows the generation of CPI stacks, which show the number of cycles lost due to different characteristics of the system, like the cache hierarchy or branch predictor, and leads to a better understanding of each component's effect on total system performance. This extends the use for Sniper to application characterization and hardware/software co-design.

Features

In addition to the main features mentioned above, we have updated the base simulation infrastructure to allow for simulating a larger set of workloads on more recent simulated hardware. Here is the full set of some of the recently added features:

- Interval core model

- Instruction-Window Centric core model, supporting in-order, out-of-order and SMT cores

- Multi-threaded application sampling support

- CPI Stacks and advanced visualization support to gain insight into lost cycles

- Parallel, multi-threaded simulator

- Multi-program and multi-threaded application support, x86 and x86-64, SSE2

- Validated against the Intel Core 2 microarchitecture (See the FAQ for details)

- Full DVFS support

- Shared and private caches

- Prefetchers

- Scheduling support

- Heterogeneous configuration support

- Modern branch predictor

- Supports parallel applications using pthreads, OpenMP, TBB, OpenCL

- Runs SPLASH-2, Rodinia, SPEC OMP and most of PARSEC (See our integrated benchmarks quick-start guide)

- McPAT integration

- SimAPI and Python interfaces for monitoring and controlling the simulator's behavior at runtime

- Single-option debugging of simulator or the application itself

- Modern Linux-OS support (Redhat EL 5,6/Debian Lenny+/Ubuntu 10.04-15.04+/etc.)

- Open source software, licensed under the MIT and the Interval Academic License

- Additional features

You can find additional information on the simulator and its components in our TACO or SC'11 paper.

Getting started

- Download the Sniper source code (Git and download options)

- Follow the Getting Started instructions

- Take a look at the Sniper Manual

- View the Frequently Asked Questions

- Review the slides from our latest tutorial

- View our most recent simulator updates

- If you are using a modern version of Sniper, please cite our TACO paper (bibtex)

Discussion list

| Subscribe to the Snipersim mailing list |

| Email: |

Please send any questions or comments to: snipersim [at] googlegroups [dot] com . You can also visit our Google Groups page to subscribe to the list and search through the archive of previous messages.

Team Members

- Trevor E. Carlson with National University of Singapore

- Wim Heirman with the Intel ExaScience Lab

- Lieven Eeckhout with Ghent University

- Ibrahim Hur with the Intel ExaScience Lab

More information